# PySpike: Agile Co-Verification of RISC-V SoC's and Beyond

LIU Yu

<liuyu@huimtlab.org>

Open Source @ Siemens 2025

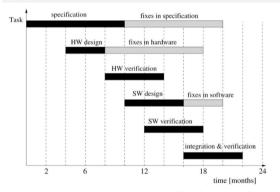

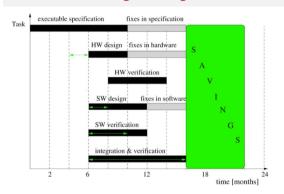

# Collaborative (concurrent) engineering 101

#### Sequential engineering

#### **Collaborative engineering**

... the executable specification may be used as a golden reference model for the software development process ... . Indeed, such a specification and the use of cosimulation tools may also help to reveal errors in the test and firmware development cycle very early. [1]

# Agenda

- Motivation

- 2 Notable Features

- Real-World Examples

- 4 Our Open-Source Playbook

- 6 Remarks and Outlook

### **Motivation**

## What Spike is all about

#### De facto standard RISC-V ISA simulator [2]

- functional model of RISC-V processors (harts) with state-of-the-art ISA support;

- originated from UC Berkeley, alongside RISC-V, actively maintained for 15+ years;

https://github.com/riscv-software-src/riscv-isa-sim

- reference model for hardware / software co-verification, e.g. differential testing [3]:

# What Spike is all about

#### De facto standard RISC-V ISA simulator [2]

- o functional model of RISC-V processors (harts) with state-of-the-art ISA support;

- originated from UC Berkeley, alongside RISC-V, actively maintained for 15+ years;

https://github.com/riscv-software-src/riscv-isa-sim

- reference model for hardware / software co-verification, e.g. differential testing [3]:

# What Spike is all about (cont'd)

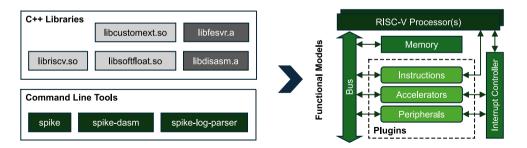

#### Spike [2], the upstream project at a glance

- C++ code base (40k+ lines), 190+ contributors, 2.9k stars on GitHub (2025/10);

- CLI tools (spike, xspike, spike-dasm, ...) and C++ libs (libriscv.so, ...);

- plugin system based on dynamic loading (dlopen) of shared objects / libraries;

## What Spike is all about (cont'd)

#### Spike [2], the upstream project at a glance

- C++ code base (40k+ lines), 190+ contributors, 2.9k stars on GitHub (2025/10);

- CLI tools (spike, xspike, spike-dasm, ...) and C++ libs (libriscv.so, ...);

- plugin system based on dynamic loading (dlopen) of shared objects / libraries;

# What Spike is all about (cont'd)

#### Spike [2], the upstream project at a glance

- C++ code base (40k+ lines), 190+ contributors, 2.9k stars on GitHub (2025/10);

- CLI tools (spike, xspike, spike-dasm, ...) and C++ libs (libriscv.so, ...);

- plugin system based on dynamic loading (dlopen) of shared objects / libraries;

```

spike \

--isa=rv64gc_xmyisa \

--priv=msu \

--extlib=my_plugin.so \

--extension=myrocc \

--device=mydev,0x20000000 \

program.elf

```

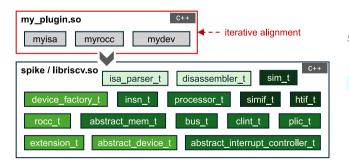

# Why Spike needs Python bindings

#### Agile co-verification calls for the feasibility of ...

- fast-prototyping custom instructions, accelerators, peripherals, ...;

- programmatically manipulating Spike for interoperation with testbenches;

- reusing small goodies like ISA-string parser, RISC-V disassembler, . . . ;

```

Python C++

my_plugin.py

pyspike

myrocc

mydev

riscv.so

riscv

myisa

spike / libriscv.so

disassembler t

sim t

isa parser

device factory

processor

simif t

htif t

insn t

plic t

abstract mem t

bus 1

extension

abstract device t

abstract interrupt controller t

```

```

$ pyspike \

--isa=rv64gc_xmyisa \

--priv=msu \

--extlib=my_plugin.py \

--extension=myrocc \

--device=mydev,0x20000000 \

program.elf

```

# Why Spike needs Python bindings

#### Agile co-verification calls for the feasibility of ...

- fast-prototyping custom instructions, accelerators, peripherals, ...;

- programmatically manipulating Spike for interoperation with testbenches;

- reusing small goodies like ISA-string parser, RISC-V disassembler, ...;

```

Python C++

my testbench.py

pyspike

my spike dut

riscv.so

riscv

my test case

spike / libriscv.so

disassembler t

sim t

isa parser

device factory

processor

simif t

htif t

insn t

abstract mem t

plic t

extension

abstract device

abstract interrupt controller t

```

### **Notable Features**

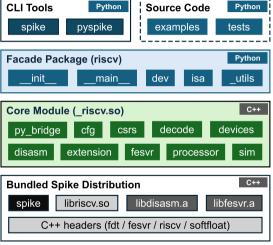

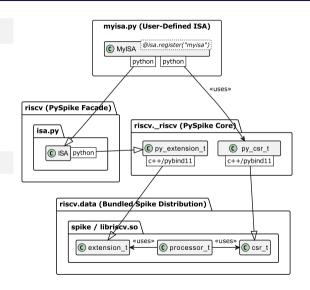

# Getting started with PySpike

#### Install PyPI package: spike

- setup virtual environment (optional):

- \$ python3 -m venv venv

\$ source venv/bin/activate

- 2 install spike package with pip:

```

(venv) $ pip install --pre spike

Collecting spike

Downloading spike-0.0.5.dev...

```

3 check availability of pyspike:

```

(venv) $ pyspike --help

Spike RISC-V ISA Simulator 1.1.1-dev

...

usage: spike [host options] <target

→ program> [target options]

```

(Supports Linux/macOS; requires Python 3.8+)

. . .

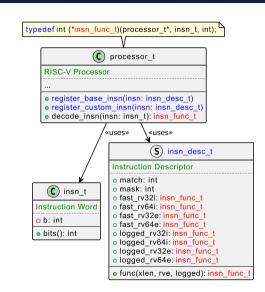

# What PySpike has to offer, exactly

#### Feature #1: Python in Spike (PIS)

write instruction / peripheral models in Python, and plug them into Spike;

```

myisa.py spike execve load program.elf pyspike dlopen dlopen call riscv.so riscv libpython3.x.so

```

```

1 # @file mvisa.pvi

2 from typing import List

3 from riscy import isa

4 from riscv.csrs import *

5 from riscv.disasm import *

6 from riscy.processor import *

8 @isa.register("myisa")

9 class MyISA (isa. ISA):

def __init__(self): ...

10

def get_instructions(self, proc)

11

→ -> List[insn desc t]: ...

def get disasms(self, proc) ->

12

def get_csrs(self, proc) ->

def reset(self, proc) -> None: ...

14

```

# What PySpike has to offer, exactly

### Feature #1: Python in Spike (PIS)

write instruction / peripheral models in Python, and plug them into Spike;

```

mydev.py

import import dlopen

pyspike

riscv

riscv

pyspike

call

libpython3.x.so

```

```

1 # @file mydev.pvi

2 from typing import Optional

3 from riscy import dev

4 from riscv.sim import sim t

6 @dev.register("mydev")

class MyDEV(dev.MMIO):

def __init__(self, sim: sim_t,

→ args: Optional[str]): ...

def load (self, addr: int, size:

\rightarrow int) -> bytes: ...

def store (self, addr: int, data:

10

bytes) -> None: ...

def size(self) -> int: ...

11

def tick(self, rtc_ticks: int) ->

None:

```

# What PySpike has to offer, exactly (cont'd)

#### Feature #2: Spike in Python (SIP)

instantiate and seamlessly integrate Spike DUT into Python testbenches;

```

testbench.pv

conftest.pv

pytest

import

pyspike

import

import

riscv.so

riscv

mydev.py

call

spike

load

libriscy.so

program.elf

dlopen

```

```

$ PYSPIKE_LIBS=mydev.py \

pytest -v testbench.py

```

```

1 # @file conftest.pv

2 import pytest

3 from riscv.cfg import *

4 from riscv.debug module import *

from riscv.sim import sim_t

7 @pvtest.fixture

def mydut():

vield sim t(

cfg=cfg_t(isa="rv32gc", priv="m",

10

→ mem_layout=[mem_cfq_t()]

0 \times 900000000, 0 \times 400000) 1),

11

halted=False.

plugin device factories=[("mydev",

\hookrightarrow ("0x20000000", ))1,

args=["program.elf"],

13

dm config=debug module config t())

14

```

# What PySpike has to offer, exactly (cont'd)

### Feature #2: Spike in Python (SIP)

reuse Spike's internal gadgets in Python, i.e., RISC-V disassembler;

```

elftools

python3.x

mydasm.py

import

load

pyspike

import

riscv.so

riscv

program.elf

call

import

spike

libriscv.so

mvisa.pv

dlopen

```

\$ PYSPIKE\_LIBS=myisa.py \

python mydasm.py program.elf

```

1 #!/usr/bin/env pvthon3

2 # @file mydasm.pv

3 from sys import argv

4 from elftools.elf.elffile import *

5 from riscv.decode import *

6 from riscv.disasm import *

7 from riscv.isa parser import *

d = disassembler t(isa parser t(

→ "rv64qc_xmyisa", "msu"))

ELFFile.load from path(argv[1])

ii s = e.get section by name(".text")

12 pc = s.header.sh addr

for op in insn_fetch_all(s.data()):

print (f"0x\{pc:08x\} (0x\{op:08x\}):",

d.disassemble(x:=insn t(op)))

pc += len(x)

15

```

# **Real-World Examples**

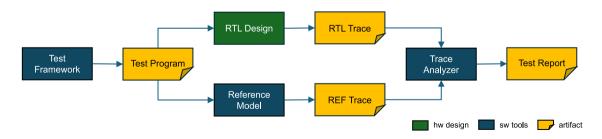

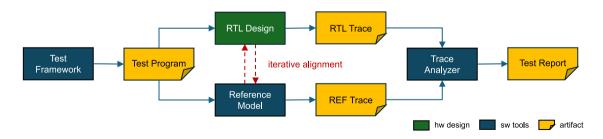

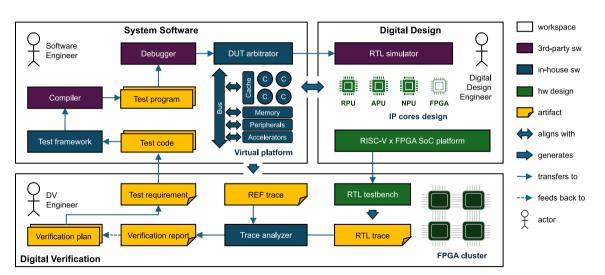

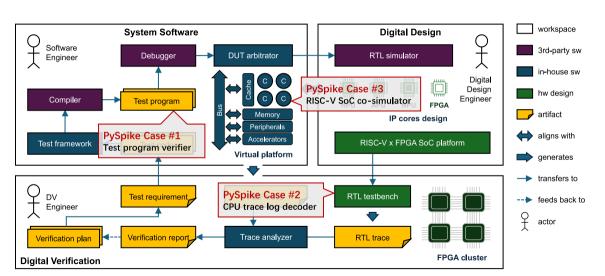

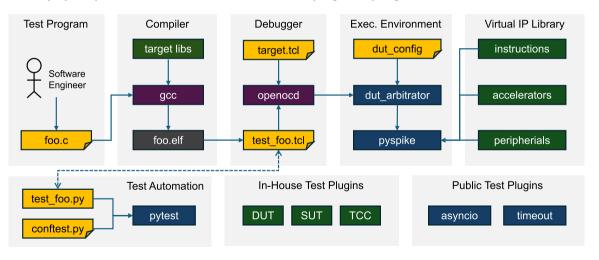

# PySpike in the big picture of co-verification

# PySpike in the big picture of co-verification

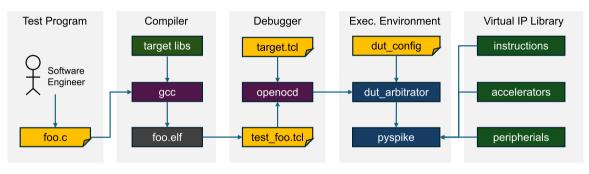

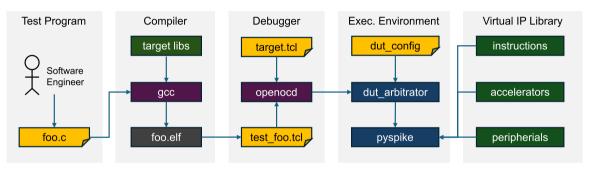

# Case #1: Continuous test program verifier

PySpike provides a reference DUT for verifying test-programs.

```

$ dut_arbitrator.py target-pyspike

Listening for remote bitbang

→ connection on port 12345.

```

```

$ openocd \

--file target.tcl \

--file test_foo.tcl

...

```

### Case #1: Continuous test program verifier

PySpike provides a reference DUT for verifying test-programs.

```

$ dut_arbitrator.py target-pyspike

Listening for remote bitbang

→ connection on port 12345.

CPU1> Hello World!

```

```

$ openocd \

--file target.tcl \

--file test_foo.tcl

...

```

### Case #1: Continuous test program verifier

PySpike provides a reference DUT for verifying test-programs.

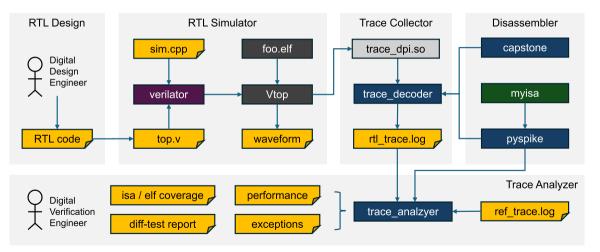

# Case #2: CPU trace log decoder and beyond

PySpike provides extensible RISC-V disassembler with top-norch ISA support.

# **Our Open-Source Playbook**

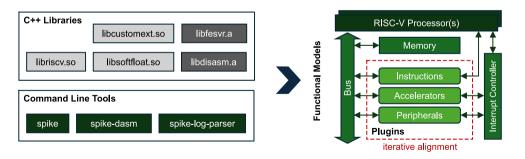

# Strategy #1: Extend, don't modify

#### Concept

- design exclusively through Spike's dlopen-based plugin system, avoid instrusive patches to Spike's code;

- bundle Spike by compiling directly from upstream source at pinned commit;

#### Rationale

- zero-effort adoption for existing Spike users, w/ or w/o custom plugins;

- minimal maintenance overhead when syncing with upstream changes;

# Strategy #1: Extend, don't modify

### **Concept**

- design exclusively through Spike's dlopen-based plugin system, avoid instrusive patches to Spike's code;

- bundle Spike by compiling directly from upstream source at pinned commit;

#### **Rationale**

- zero-effort adoption for existing Spike users, w/ or w/o custom plugins;

- minimal maintenance overhead when syncing with upstream changes;

```

$ pyspike \

--isa=rv64gc_xmyisa \

--priv=msu \

--extlib=myisa.py \

--device=mydev,0x20000000 \

program.elf

```

```

$ PYSPIKE_LIBS=myisa.py \

spike \

--isa=rv64gc_xmyisa \

--priv=msu \

--extlib=libpython3.8.so \

--extlib=_riscv.so \

--device=mydev,0x20000000 \

program.elf

```

# Strategy #1: Extend, don't modify

#### Concept

- design exclusively through Spike's dlopen-based plugin system, avoid instrusive patches to Spike's code;

- bundle Spike by compiling directly from upstream source at pinned commit;

#### Rationale

- zero-effort adoption for existing Spike users, w/ or w/o custom plugins;

- minimal maintenance overhead when syncing with upstream changes;

# Strategy #2: Upstream, don't fork

#### Concept

- proactively engage with upstream: identify hurdles early and resolve them through discussions or pull requests;

- strictly avoid maintaining divergent forks of Spike or PySpike, even internally;

#### **Rationale**

- prevent technical debt accumulation from conflicts and parallel development;

- strengthen the upstream foundation, which benefits the whole community;

#### Example (the '--device' args fix)

2023/12: Someone proposed to *fix* Spike's CLI option '--device', i.e.,

Fix Spike --device option to pass on args to downstream plugins #1522

```

$ spike --extlib=my_plugin.so \

- --device=<name> \

+ --device=<name>, <args> \

program.elf

```

The PR broke our *then-in-house* prototype PySpike for 1) the 'fixed' option assumed ','-separated values, and 2) per-device args for the same name was impossible.

# Strategy #2: Upstream, don't fork

#### Concept

- proactively engage with upstream: identify hurdles early and resolve them through discussions or pull requests;

- strictly avoid maintaining divergent forks of Spike or PySpike, even internally;

#### **Rationale**

- prevent technical debt accumulation from conflicts and parallel development;

- strengthen the upstream foundation, which benefits the whole community;

#### Example (the '--device' args fix)

# Strategy #2: Upstream, don't fork

#### Concept

- proactively engage with upstream: identify hurdles early and resolve them through discussions or pull requests;

- strictly avoid maintaining divergent forks of Spike or PySpike, even internally;

#### **Rationale**

- prevent technical debt accumulation from conflicts and parallel development;

- strengthen the upstream foundation, which benefits the whole community;

#### Example (the '--device' args fix)

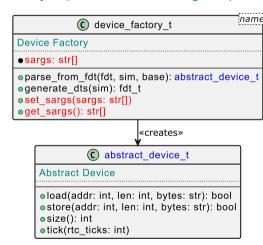

2024/04: We raised our concern to the maintainers, received positive feedback, and got our PR merged in  $\sim$ 1 week.

Counter-intuitive MMIO device arguments behavior #1652

Support per-device arguments and device factory reuse #1655

```

© device_factory_t

Device Factory

● sargs: strf[]

● parse_from_fdt(fdt, sim, base, sargs): abstract_device_t

● generate_dts(sim, sargs): fdt_t

= set_sargs(sargs: strf[])

= get_sargs(): strf[]

```

# Strategy #3: Publicize workflows

#### Concept

- share PySpike's development, testing, and packaging workflows openly;

- leverage CI/CD services to automate and enforce quality adherence;

#### **Rationale**

- foster transparency and reproducibility for external contributors and users;

- open-source software thrive on community trust, even more so for quality-assuring tools like PySpike;

#### **Example (developing workflow)**

- 1 get source code:

- \$ git clone --recurse-submodules \

git@github.com:huimtlab/pyspike

\$ cd pyspike

- 2 setup virtual environment:

- \$ python3 -m venv venv

\$ source venv/bin/activate

- install in editable mode:

```

(venv) $ pip install -e '.[dev]'

```

4 lint & test & coverage:

```

(venv) $ pytest -v

...

76 passed, 8 skipped in 9.42s

```

# Strategy #3: Publicize workflows

### Concept

- share PySpike's development, testing, and packaging workflows openly;

- leverage CI/CD services to automate and enforce quality adherence;

#### **Rationale**

- foster transparency and reproducibility for external contributors and users;

- open-source software thrive on community trust, even more so for quality-assuring tools like PySpike;

### **Example (packaging workflow)**

PySpike bundles Spike binaries as Python package data. We migrated internal build & package workflow to GitHub Actions.

Agile chip design methodology is still of limited usage due to lack of toolchain and developing framework [4]

### **Remarks and Outlook**

# We are rolling out the first *Beta* release!

#### Closing remarks and key takeaways

- PySpike opens up Spike's C++ internals for interoperation with Python scripts; we showcase PySpike's potential in boosting agile co-verification with a few examples;

- The development of PySpike is guided by our open-source playbook, promising non-intrusive design, upstream engagement, and open engineering process;

#### Future outlook and call for collaboration

- Distributing embedded toolchains via the Python Package Index (PyPI) grants wider accessibility, and brings in extra benefits like dependency management, environment isolation, multi-version coexistence, ...; we hope to explore this area in the future;

- As a language binding, PySpike needs the community's help to keep up with Spike's changes to its evolving feature set and *unstable* C++ API's;

### Who we are, and what we do

### EsionTech (中微亿芯)

- subsidiary of CETC's Research Institute 58, founded in 2013;

- headquarter in Wuxi, R&D centers in Beijing, Shanghai, Wuhan, ...;

- vendor of all-programmable and heterogeneous computing chips;

- new player in the RISC-V ecosystem, since early 2023;

#### HuiMt Labs (惠山实验室)

- affiliated with EsionTech's Beijing R&D Center;

- small group of open-source software enthusiasts;

- veterans in HW / SW co-design and co-verification;

- contributors to RISC-V tools, i.e. gcc, spike, riscv-dv, ...;

# Thank You!

#### References I

- [1] Jürgen Teich. "Hardware/Software Codesign: The Past, the Present, and Predicting the Future". In: *Proceedings of the IEEE* 100. Special Centennial Issue (2012), pp. 1411–1430. DOI: 10.1109/JPROC.2011.2182009.

- [2] Andrew Waterman et al. Spike RISC-V ISA Simulator. https://github.com/riscv-software-src/riscv-isa-sim. 2010-2025. (Visited on 10/29/2025).

- [3] William M. McKeeman. "Differential Testing for Software". In: *Digital Technical Journal* 10.1 (1998).

- [4] Yinan Xu et al. "Towards Developing High Performance RISC-V Processors Using Agile Methodology". In: *IEEE/ACM International Symposium on Microarchitecture* (MICRO). IEEE, 2022, pp. 1178–1199. DOI: 10.1109/MICRO56248.2022.00080.